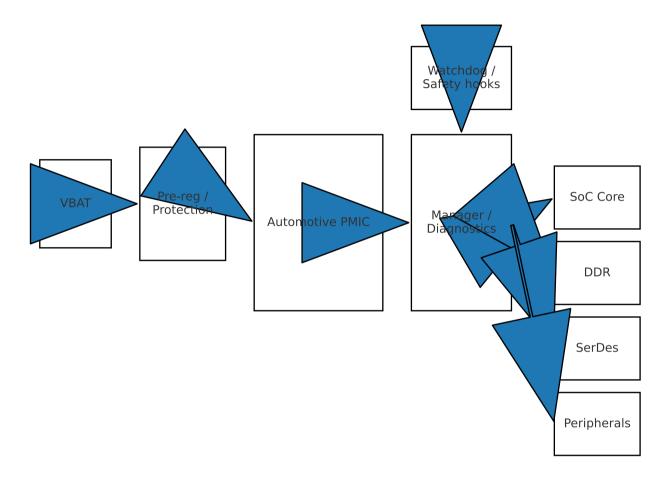

## **Automotive — Power Management Diagram**

$VBAT \rightarrow pre\text{-reg/protection} \rightarrow PMIC + manager \rightarrow SoC/DDR/SerDes \text{ (with safety hooks)}$

- Automotive PMIC + manager with watchdogs and diagnostics coordinate multi-rail SoC power.

- Fail-safe/operational paths maintain essential domains; sequencing aligns with ASIL goals and safety states.

$VBAT \rightarrow pre-reg/protection \rightarrow PMIC + manager \rightarrow SoC/DDR/SerDes with safety hooks.$

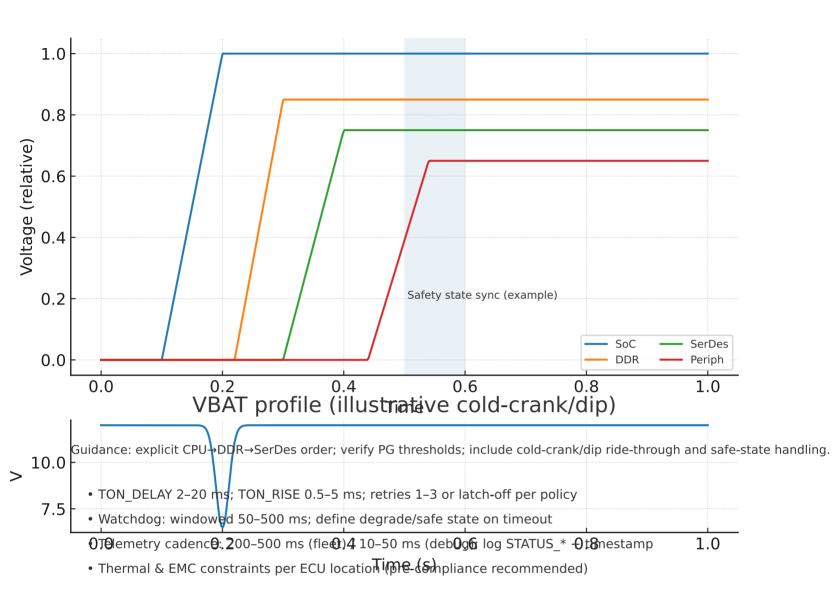

## Ordered rails & safety state sync — cold-crank/dip tests included

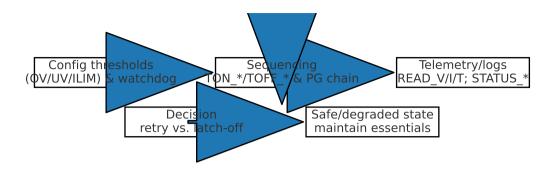

## Configure thresholds/watchdogs → READ \* & status → degrade/safe state on fault

## **AEC-Q100 Test Flow (brief)**

- Grades: 0 / 1 / 2 / 3 by temperature range

- Core items: ESD (HBM/CDM), latch-up, HTOL, temp cycling, THB/HAST, solderability, mechanical shock/vibration

- Board-level: ISO 7637-2 transients, cold-crank/dip, load dump, EMC pre-compliance

Compliance: AEC-Q100, ISO 26262, EMC pre-compliance